Source:Shutterstock

As AI chips grow larger and more complex, the limits of traditional packaging are being tested. Now, TSMC and ASE are betting big on a new frontier—panel level packaging. With technical hurdles and uncertain demand, the real question is: who will crack the code first?

Share

Link copied to the clipboard

A Chip Packaging War Brews Between TSMC and ASE

By Elaine Huangweb only

2025-07-02

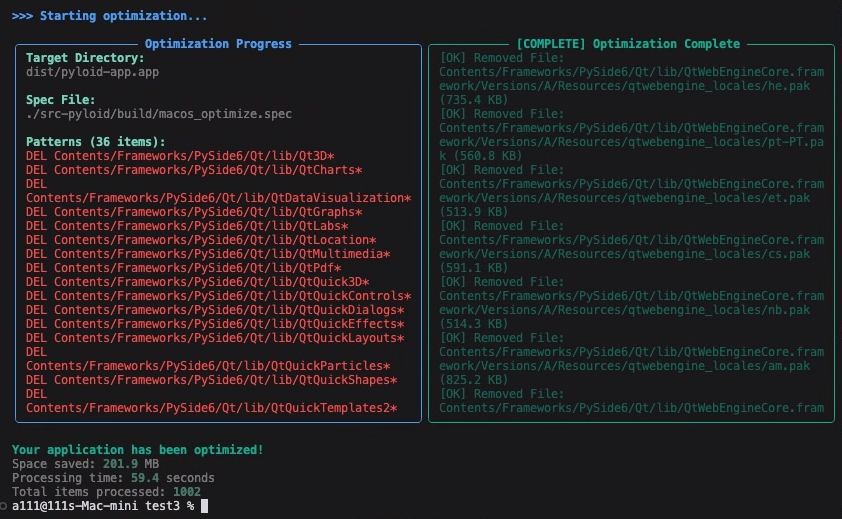

As AI chips grow increasingly complex, the packaging efficiencies of traditional round wafers have reached their limit. That’s why the world’s leading packaging company, ASE, and foundry leader, TSMC, are investing in a revolutionary technology ― panel level packaging (PLP).

Wafer packaging technology – essential for connecting and enclosing chips so they can be used in electronic devices – is currently facing very real bottlenecks.

Morgan Stanley has estimated that only 16 of Nvidia’s larger, new-generation B200 chipsets can be packaged from one circular 12-inch wafer, compared to 29 of the company’s older H200 chipsets.

Why Go from Circular to Square?

To counter this trend of diminishing returns using circular wafers, semiconductor companies are turning to panel level packaging (PLP), the core concept of which is to change the basic substrate from a circular wafer to a square (or rectangular) panel.

A veteran semiconductor analyst said the move could increase by a factor of 7 the usable area of the substrate, the material to which the elements of a semiconductor device are attached.

“The same unit of surface area can fit many more chips, leading to lower unit packaging costs,” the analyst said.

Those dual benefits align with what Tien Wu (吳田玉), the chief operating officer of Advanced Semiconductor Engineering (ASE) Holdings, was referring to when he said “customers have rigid demands.”

Betting big on the trend, ASE has already invested US$200 million in a production line to make the new square substrates and has targeted the end of the year for its first deliveries. Wu’s original strategy was to start with a 300mm x 300mm panel before gradually moving toward a more economically beneficial 600mm x 600mm mainstream spec.

Given the new technology’s difficulties, however, ASE has adjusted the dimension of the panel it expects to ship in small volumes by the end of 2025 to 310mm x 310mm. It was a decision many outside analysts saw as ASE following in the footsteps of industry giant Taiwan Semiconductor Manufacturing Co., which has adopted that 310mm x 310mm specification in its own PLP development.

One senior equipment manufacturer executive revealed that the biggest technological hurdle for panel level packaging was the tendency of large-area integrated substrates to warp during the production process, seriously affecting yields.

“The smaller the dimensions, the easier it is to control yields. Right now, TSMC is the only company with a lot of experience dealing with warpage problems,” the executive said.

That expertise has given TSMC a leg up in the technology, and the executive said TSMC was trying to replicate its successful CoWoS (chip-on-wafer-on-substrate) model in controlling the specifications and standards for another next-generation packaging technology.

Yet, panel level packaging has already seen several players interested. Aside from TSMC and ASE, panel display manufacturer Innolux Corporation has shown an interest, and Powertech Technology Inc. invested in the technology as far back as 10 years ago, setting up a panel level packaging line in 2016.

The Ultimate Question beyond Technology

Even if the technological pathway gradually leads to success, however, the common question dogging those investing in panel level packaging is: will customers go for it?

The technology has been used in the past in power management ICs, but today it has to cope with 2.5D heterogeneous integration used by high-performance AI chips made by Nvidia and AMD, which have completely different technical levels and verification standards than in past applications. Potential customers are targeting large-dimension high-end computing chips for AI servers, and Nvidia and AMD have considered the possibilities of panel level packaging.

Despite the question marks, ASE’s Tien Wu was extremely pragmatic when pondering whether his company will ultimately get a sizable piece of the market. He said simply: “To get customers to use it, it will depend on quality, yields, and price.”

Have you read?

- Taiwan Defies Global IPO Slowdown Amid AI Boom and Strategic Shifts

- The Court Document That Shook CoWoS: Why ASE Was Left Off the Billion-Dollar Table

- Taiwan Leads Global Push for Democratic Alliance on Chips, AI, and UAV

Translated by Luke Sabatier

Uploaded by Ian Huang

Share

Link copied to the clipboard

Subscribe to CWE Newsletter (every Thursday)

Stay abreast of what's happening in Taiwan with our weekly digest.

.png)