As RISC-V turns 15, we explore how a summer grad project became the official compute architecture of nations – and why its story is just beginning.

By James De Vile, Editor, RISC-V International

May 2010. UC Berkeley student Andrew Waterman has just sent an email to his professors. After months of auditioning different instruction sets for a 3-month project, he has reached a conclusion:

They should revive near-dead microprocessor architecture DEC Alpha.

“I couldn’t see us creating something new,” says Waterman. “It wasn’t about the ISA design – that in itself is an intellectually stimulating, creative, technical task. But bringing up compilers, operating systems, porting a universe of software? I saw a multi-billion dollar endeavor far outside the scope of a handful of academics.”

For professor Krste Asanović though, it was principle over preference: no existing ISA could deliver what they needed. “There wasn’t an option, to my mind,” says Asanović. “Alpha was a speed demon, but had many architectural problems. I just didn’t want that baggage.”

The team, Asanović postulated, had spent far too long stuck between prohibitive commercial ISAs and those that were less restrictive – yet flawed or fading. Moore’s Law was slowing and Dennard scaling was ending, requiring specialization, customization, and parallelism. And for these, they needed a clean slate.

The discussion between Asanović, Waterman, and fellow grad student Yunsup Lee played out over a few further emails. Finally, on May 18, 2010, Waterman capitulated–embracing the risk of a new RISC.

As an aside, let me address the RISC/risk pun. The gift that keeps on giving for headline writers, many are unaware they’re borrowing an intentional wink from the father of RISC himself, Dave Patterson. “We figured government agencies renowned for funding high-risk, high-reward bets might look on us more favorably,” he tells me.

Patterson’s bet paid off, and he created the first RISC architecture in 1980. In 2005, he founded the Parallel Computing Laboratory (Par Lab) at UC Berkeley, and five years later RISC-V became the fifth major RISC ISA to come out of the university under his mentorship.

15 years since that Tuesday in 2010, RISC-V is not only the third largest ISA on earth, it has landed on the moon. High risk? Perhaps. High reward? Absolutely.

Finding a Niche

Here are two further common assumptions about RISC-V: that the team set out to build an open-source architecture first and foremost, and that it had to fight its way out of academia.

“We stipulated it had to be easy to build by a small University team, it had to be efficient, and it had to be easily extensible” says Asanović. “The requirement for it to be open was driven by the desire to share what we built with our friends via the Berkeley software distribution license. We wanted to move the academic computer architecture community back towards real, RTL hardware designs, away from C models of something that may or may not work in the real world.”

And for the years that followed, RISC-V was purely a tool for classes and research into parallel computing and processor design. But getting academia outside Berkeley to take note was harder than expected. “Academics were very skeptical,” says Asanović. “To them, it was just another RISC ISA to learn. The fact that it was an open standard wasn’t interesting to them – they wanted to teach what the industry was using. So they kept plowing on doing x86 stuff.”

You know the ‘RISC-V Four’ – Asanović, Waterman, Lee, Patterson. A name you may be less familiar with is independent computer architect and fellow Berkeley alumnus John Hauser. Asanović calls him the fifth Beatle.

“We thought we’d need to start pushing this thing hard. Apparently, we’d massively underestimated the hunger for an open ISA”

“Hauser has been instrumental in shaping the ISA” says Asanović. “The ecosystem owes him for the hypervisor in 2020 and advanced interrupt architecture (AIA) in 2023. But we also probably owe him an apology – because when he told us RISC-V was going to be big, we just weren’t ready to believe him.”

The first version of the RISC-V instruction manual was published in May 2011. Yet the team only realized they had users outside of Par Lab after tinkering with the ISA design over the course of a few UC Berkeley classes. Suddenly, people on the other side of the world were demanding to know why they’d changed something.

“We knew there was a niche,” says Asanović. “We just had no idea that we’d be filling it for others, too. A lot of people were focused on the technical stuff. Is this better than other ISAs, technically? In hindsight, it was glaringly obvious that RISC-V would succeed not on its technical merits but because it was open. The real innovation was the business model.”

“There was no push from us,” says Waterman. “If anything, a gentle nudge came through us finishing the project in 2014. It’s done, we said, we’re not going to mess with it anymore. After that, things really started to kick off.”

The Pull of Industry

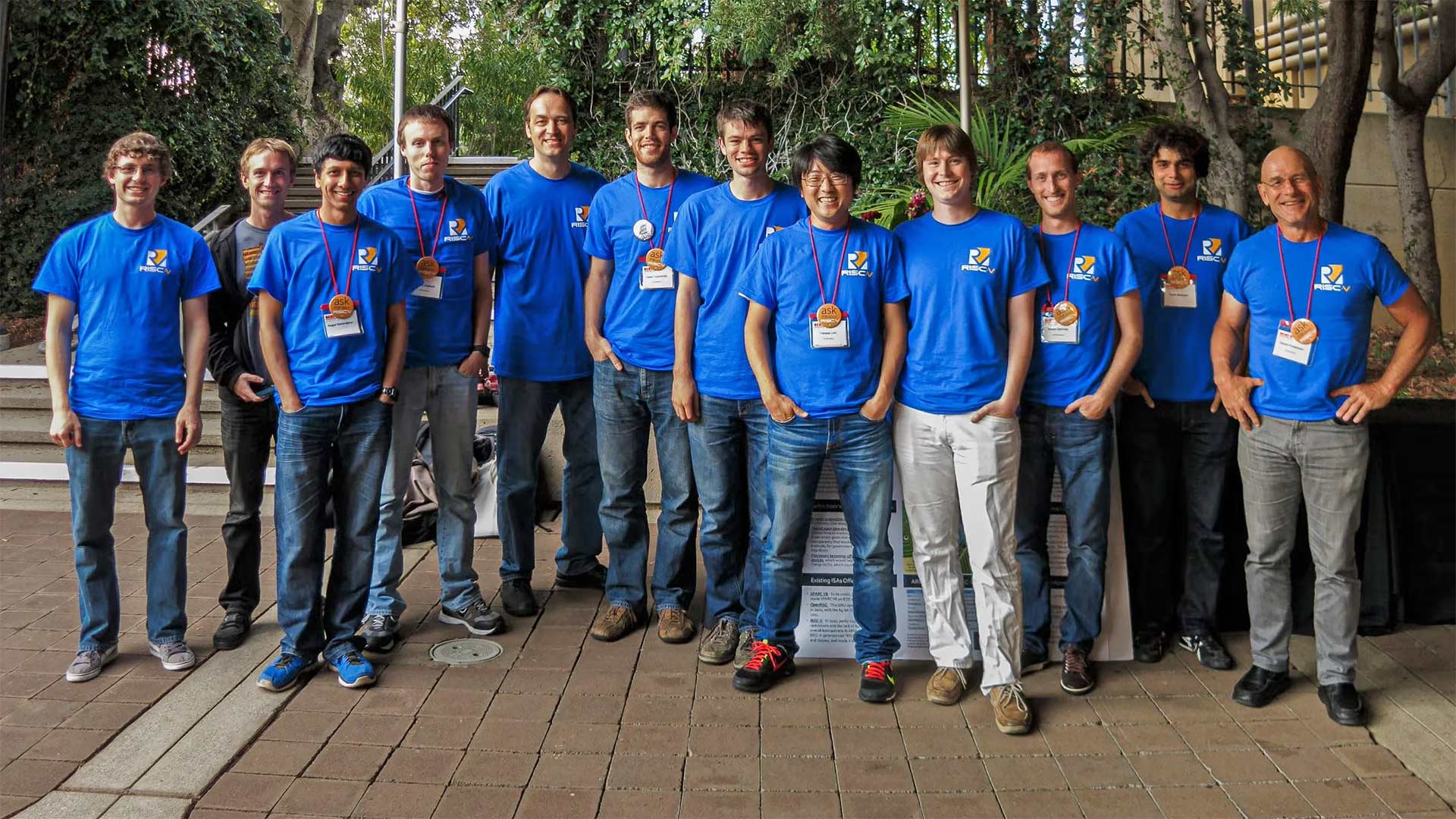

Hot Chips 2014. L>R, 5 – Krste Asanović, 8 – Yunsup Lee, 9 – Andrew Waterman, 12 – Dave Patterson

The 2014 IEEE Hot Chips 26 Symposium, held August 10-12 2014 in Cupertino, was eye-opening. “We were very surprised at the pull from industry,” says Asanović. “We attended thinking we’d need to start pushing this thing hard. Apparently, we’d massively underestimated the hunger for an open ISA.” By the time the team held the first RISC-V workshop in Monterey in January 2015, the balance had truly shifted. “We anticipated a small academic crowd,” he says. “40 different companies attended.”

But openness wasn’t the only appeal. Another key complaint the team heard was in the inflexibility of commercial ISAs. The primary benefit of RISC-V to industry was flexibility, not cost. Yet RISC-V’s openness didn’t just slash costs – it cut red tape. “Startups were telling us it took up to two years to get a contract signed, which killed them,” says Asanović. “With RISC-V they could be using it that afternoon. We didn’t have to convince anyone that this was a good thing.”

Fuelling the heat that year was a seminal positioning paper published by Asanović and Patterson, titled “Instruction Sets Should Be Free: The Case For RISC-V”. In it, they doubled down on the open message, likening it to open standards such as TCIP/IP, Ethernet, the C language, and Linux.

For industry, the paper hit home. Rumble Technologies’ Mike Aaronson read it and switched an FPGA-based camera project from MIPS to RISC-V in three weeks. This became the first-ever commercial product to use RISC-V.

At the 4th RISC-V workshop in July 2016, NVIDIA announced plans to replace its proprietary Falcon cores – used for tasks like power management and security inside its graphics processing units (GPUs) – with RISC-V, driven by a need for 64-bit. This move, which culminated in one billion cores shipped in 2024 alone, may not have grabbed headlines at the time. But it mattered: a top-tier semiconductor company was trusting RISC-V for critical internal functions.

A few months later, the 5th RISC-V Workshop was held at a Google facility in Silicon Valley. “The turnout from industry was far greater than previous workshops, representing 107 companies and 30 universities,” says Larry Lapides, Executive Director of RISC-V Tools Business Development at UK-based Imperas, now part of Synopsys. “The talks and conversations I held there convinced me that RISC-V was absolutely ripe for industry adoption.”

Now recognizing the opportunity ahead, Larry and CEO Simon Davidmann positioned Imperas as a leading force in RISC-V’s journey—dedicated to shaping its commercial future and supporting the ecosystem’s growth. Imperas’ commercial software tools, including simulators and verification suites, have since been widely adopted across the ecosystem, accelerating maturation and establishing best practices for design verification.

Education’s Eventual Embrace

With RISC-V momentum reaching critical mass, academia finally acknowledged industry demand – and embraced RISC-V as the architecture to teach.

“From top to bottom, we’d transitioned all of our course material to RISC-V,” says Asanović. “And as is common in academia, institutions ‘borrow’ from leading universities. It’s easy enough creating slides; building labs takes a lot of energy, effort, and engineering work. Finally, when our full set of resources started showing up in other university programs, we knew we’d made an impact.”

Through osmosis, RISC-V re-entered academia. Institutions globally – including MIT, ETH Zurich, and the University of Bologna – adopted RISC-V in their teaching and research programs, leveraging its open-source nature to develop course materials and laboratory exercises.

“It made a lot of sense to migrate from OpenRISC to RISC-V, due to the much larger community around it”

Back in 2013, ETH Zurich and the University of Bologna had teamed up to launch a new open-source initiative called PULP (Parallel Ultra-Low Power), based on OpenRISC. The project was led by Professor Luca Benini – Chair of Digital Circuits and Systems at ETH Zurich and professor at the University of Bologna, alongside Frank K. Gürkaynak, a senior scientist at ETH Zurich and director of its Microelectronics Design Center, and project lead Professor Davide Rossi.

“The initial idea of PULP was not to design our own processor cores,” reveals Gürkaynak. “But after a few discussions with proprietary core vendors, we realized that we needed to have open access to the cores to be able to experiment and share our changes with other partners.”

The PULP team had been struggling to achieve the performance they needed with OpenRISC. Then, Rossi attended the first RISC-V Workshop and Boot Camp in Monterey in 2015. “I realized it made a lot of sense to migrate from OpenRISC to RISC-V, due to the much larger community around it,” he says. “By the end of 2015, we had migrated all of our cores to RISC-V.”

“For us that are interested in researching new architectures and new possibilities, being able to develop, experiment, and share a processor implementation so freely has opened many doors,” explains Gürkaynak. “We’ve been able to collaborate across academia and industry much faster based on our widely-used, permissively licensed implementations. RISC-V has been good for us – and we’ve been good for RISC-V.”

Leaving the Lab

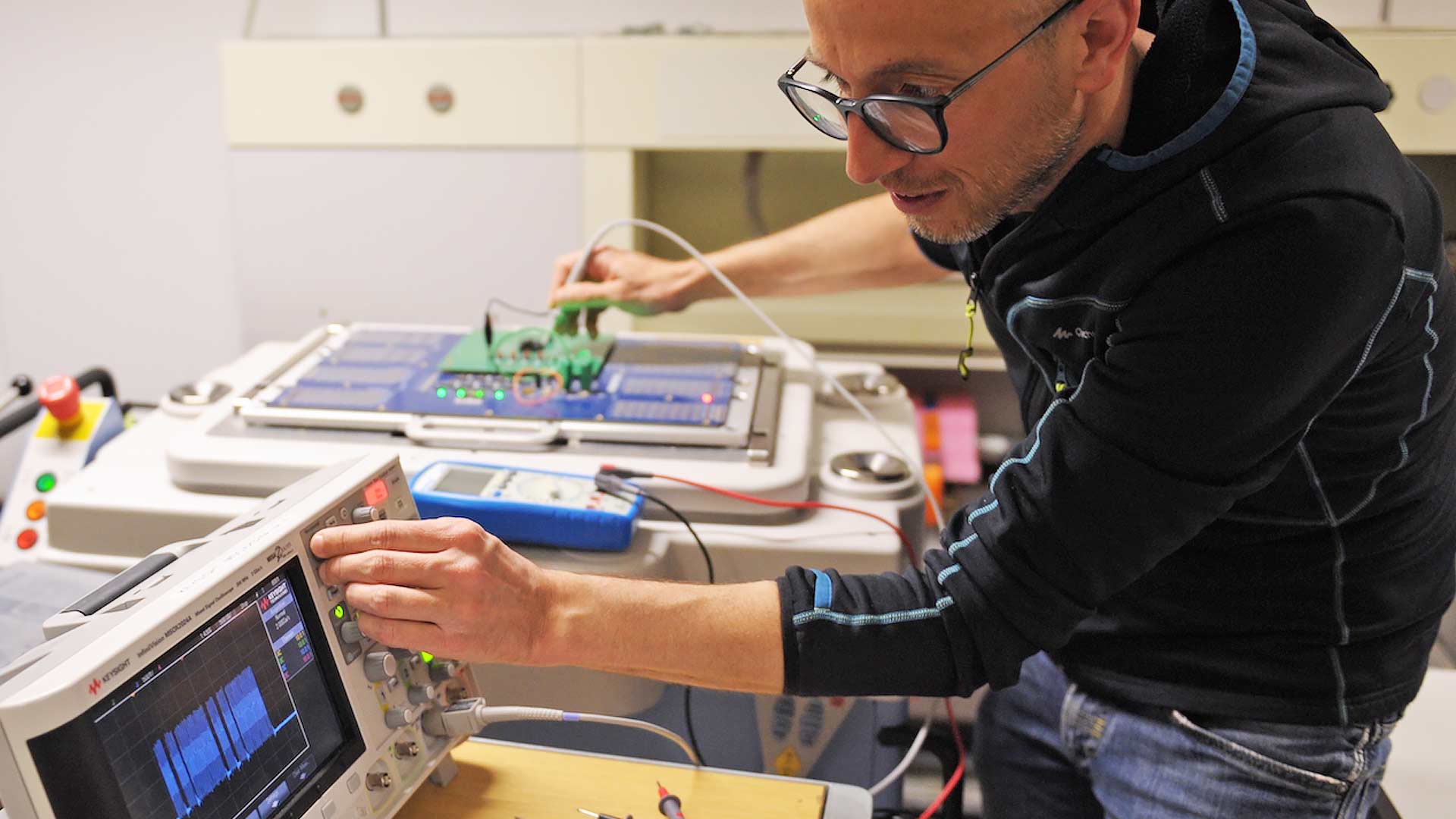

Antonio Pullini getting the first signs of life out a RISC-V based IoT core at ETH Zürich

With RISC-V going global, the time had come to break it out of Par Lab. “Everyone knows grad projects die when students file their dissertation,” says Waterman. “We needed something more stable to house the standard.”

So in 2015, the RISC-V Foundation was founded to promote openness, neutrality, and prevent fragmentation, while establishing the ISA as a legal entity. And, of course, to ensure its continued growth should academia move on to new pastures. One of the key figures in this transition was Rick O’Connor, who played a central role in navigating the early governance model and, as founding Executive Director of the Foundation, helped lay the groundwork for an industry-friendly structure. Rick had been a vocal proponent of moving RISC-V out of the lab into its own foundation, and his leadership was instrumental in bridging the gap between academic origins and commercial adoption, ensuring the foundation could scale with growing interest.

“Rick’s idea was that companies that joined within the first year would be founding members; working with us to define the membership bylaws and to figure out how it was all going to run” explains Asanović. “I expected half a dozen sign-ups, but we ended up with 42 founding members – including Google, NVIDIA, IBM, Western Digital, Qualcomm, and Microsemi. Suddenly, we had 42 legal departments – some with entire floors of legal teams – poring over the fine print.”

“The Foundation was designed to align everyone, but it was no small task,” explains Jeffrey ‘Jefro’ Osier-Mixon, the Foundation’s former Board Secretary, now Distinguished Community Architect, Office of the CTO, Red Hat. “We tried very hard to make it as open and transparent as possible.”

There had to be a membership agreement in place, purely for the providence, he continues. “There’s also some language deep within that protects patents between members. Explaining to the community why it was needed (and why it needed to be signed) wasn’t always easy, but it was crucial to ensure trust and collaboration among diverse stakeholders.”

In parallel, Asanović, Waterman, and Lee began working on commercializing RISC-V through SiFive. This new company, they imagined, would deliver bespoke silicon for customers, tailored to specific applications. Each project would be unique, capital-intensive, and with limited opportunity for reuse – drawing on not only RISC-V but all the other innovations they’d dreamt up in Par Lab.

“We didn’t have a pitch sheet or even a business model figured out before they gave us Series A funding,” says Asanović. “It was a case of ‘look, you guys seem smart, don’t let us down.’” But the team didn’t have the luxury of being a stealth startup. Everyone was watching to see what the RISC-V guys did next. Immediately, they had a dozen large companies asking them for reusable core IP blocks.

“We thought about it and decided it would help the adoption of RISC-V if we did what they wanted,” says Asanović. “It might also help us land and expand into these companies to see what other projects we could get involved with.” After making a handful of customized cores in the embedded space, SIFive pivoted into an IP business.

A Growing Ecosystem

From 2015 to 2019, commercial demand began to shift toward production-ready IP. While the ISA’s open-source nature empowered innovation, especially in academia, the burden of functional verification – often consuming 75 percent of development time and cost – remained a significant barrier to entry, especially at advanced process nodes: designing something at 3nm requires design teams of perhaps thousands of engineers working tens of thousands of hours and costing hundreds of millions of dollars just for the functional verification step.

Rather than reinvent the wheel, companies began to opt to license proven, pre-verified cores from emerging commercial IP vendors. For a number of these vendors, RISC-V had driven a significant transformation of their business model. “We evolved from a pure-play EDA (Electronic Design Automation) company into one that combines both IP and EDA expertise,” says Codasip CTO Zdenek Prikryl. “This shift has positioned us to lead in the design and customization of RISC-V processors – delivering true heterogeneous and application-specific compute, as well as enabling us to explore and implement community innovations such as CHERI (Capability Hardware Enhanced RISC Instructions) security extensions.”

Andes Technology also embraced RISC-V at the RISC-V Workshop in 2016, after almost a decade of developing proprietary embedded IP. “RISC-V aligned perfectly with our strengths in extensibility, customization, and real-time computing,” says Andes chairman and co-founder Frankwell Lin. “It wasn’t just the technical merit that impressed us, but also the potential to be part of a vibrant, global community that shares knowledge, co-develops standards, and enables faster industry adoption.”

At the same RISC-V Workshop, storage titan and founding member Western Digital (WD) announced that it was transitioning its processor cores to RISC-V. And in 2019, WD CTO Martin Fink announced a goal to ship over one billion cores per year to RISC-V – channeling IBM’s historic $1 billion investment in Linux in 2000. This commitment marked the most significant public endorsement by an established volume manufacturer to date, and WD followed through.

Speaking of Linux, it was around this time that the RISC-V and the Linux foundations announced a joint collaboration agreement to accelerate development and adoption. Calista Redmond, succeeding Rick O’Connor as CEO, oversaw the 2020 transition of the Foundation into the RISC-V International association (RVI), now headquartered in Switzerland in pursuit of unfettered access and geopolitical neutrality. As part of this transition, RISC-V International began leveraging the Linux Foundation as a service provider for infrastructure, governance, and community support.

Redmond’s tenure ushered in a new era of strategic global growth. She spearheaded initiatives that expanded RISC-V’s footprint into new regions and industries, while positioning the architecture as a pillar of digital sovereignty on the world stage. As a result, this period marked rapid growth in industry participation and a nascent commercial ecosystem, despite global disruption from COVID-19 and the resulting chip shortage.

Until his retirement in 2023, Rick O’Connor went on to be President and CEO of the OpenHW Group – a newly-founded not-for-profit, global organization fostering developer collaboration in pursuit of both commercial and academic adoption of RISC-V hardware. The OpenHW Group now curates its own family of RISC-V cores, aiming to provide industrial-grade open-source hardware upon which the community can sprinkle its own breakthrough IP and unique innovation on top.

“Prior to RISC-V, CPU IP was locked behind restrictive NDAs, high NRE costs, and royalty models, making open collaboration at the silicon level almost unimaginable,” notes OpenHW CEO Flo Wohlrab. “Today, because of RISC-V and OpenHW, we’re seeing a global ecosystem where businesses are not only adopting open cores, but actively building products and creating entirely new markets around them.”

RISC-V Sans Frontières

The RISC-V Brazil event in June 2024

“You expect a national bird or flag – but a computing architecture? That’s remarkable”

The past five years in particular have seen RISC-V establish itself firmly on the world stage. “RISC-V is now a truly global entity,” says Osier-Mixon. “Nations are engaging with RISC-V at a governmental level, pursuing digital sovereignty. Fifteen years ago, who would have imagined countries like Brazil and India adopting it as central to their national computing architecture? You expect a national bird or flag – but a computing architecture? That’s remarkable.”

But these developments were no accident. Redmond steered RVI doggedly toward becoming a neutral ground for open compute – opening dialogue with national governments and policymakers and aligning the architecture with strategic technology independence initiatives.

Brazil has strengthened its role in the RISC-V ecosystem, becoming a premium member of RISC-V International in February 2024. In July 2025, São Paulo will host the second RISC-V Brazil event, continuing a strategic push for open-standard innovation in Latin America.

India’s involvement in RISC-V had begun in 2014 with the Shakti project, initiated by IIT Madras and supported by the Ministry of Electronics and Information Technology (MeitY). This academic effort laid the groundwork for the country’s broader RISC-V ambitions. In 2022, MeitY launched the Digital India RISC-V (DIR-V) Program to drive the development of indigenous RISC-V processors for strategic and commercial applications. This has become a key component of India’s Atmanirbhar Bharat Abhiyaan, which translates to a self-reliant India campaign.

“Even from the very early days, with countries such as India, there was awareness that RISC-V would be really good for national security. They didn’t have to depend on a foreign supplier for their critical compute infrastructure,” says Asanović.

The past 15 years have also seen a significant increase in awareness around state-sponsored cyberattacks. Concerns over IT security have become far more pronounced. As a result, nations are prioritizing their own national security interests, recognizing that achieving this requires building trusted and sovereign implementations of hardware.

“If it’s proprietary and owned by a different state actor, the trust isn’t there” says Asanović. “You need an open standard – that way you can re-use software and run it on your own, trusted hardware.”

China, in particular, has embraced RISC-V as a pathway to architectural sovereignty. In 2019, Alibaba’s chip subsidiary, PingTouGe, announced its first RISC-V project – XuanTie 910, a commercial multi-core 64-bit processor with vector extension that brought RISC-V into the Chinese technology mainstream and secured a stable future for Chinese chipmakers. A year later, the Institute of Software at the Chinese Academy of Sciences (ISCAS) launched the country’s first openEuler Linux distribution for RISC-V.

ISCAS has also made major strides in virtualization, contributing heavily to efforts like Kata Containers and Cloud Hypervisor. Their latest milestone – a new LLVM-based RISC-V image with vector support, has been successfully tested on the K1 development board – marking a significant leap forward for openEuler, China, and the wider RISC-V community.

Vertical Alignment

The ratification of the application-level RVA23 profile last year marked another milestone for the architecture. With key components – vector, hypervisor, and cryptology – baked in, RVA23 is already proving crucial in scaling RISC-V into domains such as AI, automotive platforms, and rich operating system (OS) environments such as Android.

“RVA23 was a major milestone for me because it meant we’d passed the point of asking ‘can RISC-V do this?’ – it can”

“Profiles are the foundations of application and systems software portability across RISC-V implementations,” says Andrea Gallo, newly appointed CEO of RISC-V International. “A large software ecosystem is only possible with a standard profile for software vendors to target and within which multiple suppliers can work together.”

As foundational gaps close, the focus is shifting towards enabling full ecosystems in specific vertical markets, each with distinct needs: software frameworks, toolchains, real-time capabilities, safety standards, and core implementations optimized for performance, power, and area.

“RVA23 was a major milestone for me because it meant we’d passed the point of asking ‘can RISC-V do this?’ – it can,” says Asanović. “The ISA is mature, toolchains stable, and core capabilities robust.”

However, he says, the profile is generic – it isn’t tied to any particular vertical segment. As higher-capability cores become available and people become more comfortable with basic RISC-V foundational components, we’ll see new ecosystems emerging around each vertical.

However, we shouldn’t rush to create profiles for every vertical, he cautions. “Each of these verticals needs a complete solution. For example, we’ll identify exactly what’s needed to make a successful automotive MCU profile, and gather all the necessary components. The worst thing we can do is deliver 90 percent of a solution for 100 markets. It’s much better to have 100 percent of the solution for 10 markets.”

“This is what makes the 15th Birthday of RISC-V such an inflection point,” says Gallo. “The years ahead will see the RISC-V ecosystem move into a new phase where performant cores and broader industry confidence enables targeted ecosystem development in domains like space, automotive, data centers, embedded systems, high performance computing (HPC), and security.”

AI takes Center Stage

RISC-V also accelerates the design of workload-driven processors. Chip designers can tailor their designs to specific application and domain requirements, enabling optimization for diverse compute-intensive AI workloads, from generative AI to autonomous navigation.

“RISC-V makes it possible to integrate specialized instructions tailored for machine learning (ML) and other data-intensive tasks directly into the processor,” says Gallo. “This facilitates the development of dedicated in-core and near-core hardware accelerators for specific operations commonly found in these workloads, such as matrix multiplication or tensor operations.”

AI, says Gallo, will be the glue that holds them all together. “It cuts across every industry. That’s why we’re putting so much focus on enabling AI, from software down to the base ISA. No matter the vertical, from car to supercomputer, we want developers to have the tools and intelligence they need.”

RISC-V has a modest goal: Become the industry-standard ISA for all computing devices, in all industry verticals. When I ask people what they think stands in the ecosystem’s way, I get the same answer – software.

“The biggest challenge for RISC-V in the next 15 years will be to create a mature software ecosystem – especially for HPC,” says Davide Rossi, Associate Professor at the University Of Bologna.

“It’s a bit of a chicken and egg situation,” says Asanović. “There’s no point building a core optimized for some vertical market segment if there’s no software to run it, but nobody’s going to write software for a core that doesn’t exist. So the industry needs to co-evolve.”

“Probably the last dominoes to fall are going to be application servers and mobile devices, simply because the installed software base of those two domains is truly enormous,” says Waterman. “First we’ll see RISC-V used in more specialized tasks within these devices – such as network packet processing, AI-optimized traffic routing, power management, and security.”

“Magic happens when communities unite to solve tough problems”

Waterman’s 2010 prediction that software would be RISC-V’s biggest hurdle still holds true. But unlike the early days, this isn’t just the domain of a handful of academics. Today, ambitious projects like the RISC-V Software Ecosystem (RISE) project are laying the foundation for commercial success in establishing robust, scalable software ecosystems for application processors with production-grade toolchains, runtime environments, virtualization, and OS-level integration.

Founded in May 2023 by Qualcomm, Google, Intel, NXP, Nvidia, Red Hat, Samsung and others, RISE has since advanced upstream open-source software projects through member contributions, and through funding more than $1 million in externally awarded contracts.

“Magic happens when communities unite to solve tough problems,” says Amber Huffman, RISE Governing Board Chair. “We formed RISE in recognition of the clear need for collaborative efforts to deliver performant and commercially ready software for RISC-V.”

Like Asanović, Huffman sees this as a chicken and egg problem. “To be successful, a new ISA and its features must be supported by robust low-level software,” explains Huffman. “But that software often won’t be built until the platform is already adopted. RISE is proud to partner with RISC-V International to help break this cycle.”

To help the developer ecosystem, RISE published a RISC-V Optimization Guide and recently launched the RISC-V Developer Appreciation Program to reward developers that port, test, and release open-source projects on RISC-V. Just two of the many contributions by the RISE community that have advanced open-source software for RISC-V.

With the software stack fully established, RISC-V will truly be inevitable. “The next 15 years will see RISC-V truly cross the chasm into mainstream adoption,” says Codasip’s Zdenek Prikryl. “I envision a future in which RISC-V-based desktops and laptops sit alongside other architectures, having matured to be on par with established ecosystems. While we’re already seeing progress toward this vision, I’m confident that the most exciting developments are still ahead.”

“15 years from now, the OpenHW Foundation will be the go-to place for high quality, open source cores,” says OpenHW’s Flo Wohlrab. “Chipmakers will use these as Linux is used today in the industry, by everyone – with a huge, driving ecosystem allowing more and faster innovation.”

V is for Vector

Krste Asanović talking at RISC-V Summit Europe 2025 last week

It’s a not-particularly-well-kept secret that the “V” in RISC-V also nods to vectors – reflecting Asanović’s long-standing vision for vector processing as a core capability of the ISA. “It’s just great to see everyone excited about vectors again,” he says. “My thesis chip in the early 1990s was a vector machine for running neural nets.”

This intention later materialized in the RISC-V Vector extension (RVV), a key differentiator for RISC-V compared to other ISAs. RVV provides scalable, flexible vector capabilities aimed at everything from edge devices to HPC.

“I think we’re ahead of other architectures when it comes to supporting high-intensity numerical computation with vector and matrix processing,” says Asanović. “Just look at how we designed the vector ISA. I’m biased, since I led much of that work, but it’s far more scalable than the vector extensions in other ISAs, which haven’t gained much traction.”

Bias or not, the fact remains: RISC-V benefits from its clean slate, free from legacy architectural baggage. This, combined with powerful vector and matrix extensions, positions RISC-V CPUs to handle tomorrow’s demanding AI workloads without help from accelerators. GPUs and NPUs serve important roles in AI, but it’s the CPU that drives most AI processing today.

The RISE project recently formed a workgroup focused on AI/ML as a collaborative space to ensure widely used AI software (e.g., PyTorch CPU, Llama.cpp, GGML, LiteRT, OpenBLAS) are performant on RISC-V hardware. In China, ISCAS quickly embraced RVV, introducing key performance improvements to multimedia frameworks and open-source projects like ffmpeg, PipeWire, and Tesseract.

“The increased focus on AI is also making it easier for RISC-V to catch up to its contemporaries,” says Waterman. “More and more software comes in the form of frameworks that are a bit more portable than an entire universe of random software.”

As RISC-V performance increases, so does the ability to migrate AI workloads from the cloud to the edge. One company exploring these possibilities is ESWIN Computing, which recently ran the DeepSeek LLM locally on its EIC77 series RISC-V based development boards.

“RISC-V enables us to innovate at the chip architecture level,” says Dr. Ning He, SVP and CTO of ESWIN Computing. “Its open architecture facilitates profound cooperation between CPU and AI accelerators, such as NPUs and TPUs. This architecture supports the collaborative design of heterogeneous computing, effectively expediting deployment of AI at the edge. And the ability to offer different vector widths according to specific needs enables us to achieve a higher level of customization than ever before.”

“HPC Is All Around Us”

The ratification of RVV v1.0 represented a considerable breakthrough in HPC – with European projects like the European Processor Initiative (EPI), EUPilot, and Digital Autonomy with RISC-V in Europe (DARE) all embracing the extension’s benefits for supercomputing and beyond.

“The notion that other people would attempt to build supercomputers with RISC-V still blows my mind”

“Given we didn’t have any particular ambitions for the ISA to be used outside of Berkeley, the notion that other people would attempt to build supercomputers with RISC-V still blows my mind,” says Waterman. Yet not only have the attempts been made – their resulting success has made HPC one of the architecture’s most exciting and unexpected frontiers.

“Nowadays there’s no doubt that RISC-V is HPC-capable,” says Teresa Cervero, leading research engineer at Barcelona Supercomputing Center (BSC). “In the past 5 years especially, commercial RISC-V HPC platforms have been reducing the performance gap with more mature architectures exponentially.”

RISC-V offers a unique opportunity to redefine the future of HPC, says Cervero. “We must explore, leverage, and exploit the strengths it offers compared to other architectures, rather than repeat what they have been doing. Future supercomputers will be more heterogeneous and with higher levels of complexity, and RISC-V brings the possibility of tackling this differently.”

Cervero also takes pains to point out that I’ve fallen into the trap of equating HPC with supercomputers. In fact, she says, HPC is all around us – any system handling complex tasks or massive data at speed qualifies. And a major frontier for HPC is automotive, where the shift to software-defined vehicles (SDVs) demands flexible, scalable compute.

Software-Defined Vehicles

Infineon Technologies is harnessing RISC-V for a new generation of automotive microcontrollers (MCUs). Image credit: Infineon

As the automotive industry evolves, RISC-V is taking strides to embed itself in the vehicles of the future. Its open, modular, and customizable design means automakers can adapt quickly, cut costs, and build exactly what they need – without being locked into someone else’s roadmap. The ecosystem is already delivering FuSa certified compilers, software development tools and components ready for use in automotive applications along with rich operating systems and virtual platforms.

“Virtualization and standardization will be key to delivering an next-gen automotive MCU”

Perhaps most importantly, it’s enabling carmakers to reduce time to market. “Automotive has historically been an extremely traditional industry,” says Osier-Mixon. “Carmakers’ definition of rapid change has meant innovating every five to ten years.”

“With the electric-electronic vehicle revolution, that iteration needs to come every two to three years,” says Thomas Schneid, Senior Director of Software at Infineon Technologies. “We need a major reduction in complexity – architecture, software, connectivity, and networking – and a weight reduction of the wiring harness.”

How, I ask him, do we achieve that list? “Virtualization and standardization will be key,” Schneid continues. “RISC-V will enable Infineon to deliver a scalable and cost-efficient way to implement the diverse computing requirements of future automotive microcontrollers, offering a single architecture that can be used for multiple processing cores, enabling dependability, scalability, and innovation through its open and inclusive nature.”

It’s a market segment that demands dependable, secure, and safe solutions based on the benefits of open-standard hardware and software. The beauty of RISC-V, says Schneid, is that we can do all of that with a single architecture. “This is a transition from proprietary closed solutions owned by single entities to an environment built on strong collaboration between many key market players.”

Establishing a high-performance automotive RISC-V reference platform over the next few years will reduce dependency on proprietary architectures and ensure long-term competitiveness. The Chips JU projects TRISTAN and ISOLDE, designed to mature and industrialize the RISC-V ecosystem in Europe, along with the dedicated automotive RISC-V roadmap, are key enablers – aligning stakeholders in building scalable, standards-based software and hardware platforms, tailored to Europe’s strategic needs in next-generation mobility.

Reaching for the Stars

A Mars Rover. Credit: European Southern Observatory

Supercomputers and autonomous vehicles aren’t the only targets for HPC. Last month, the European Space Agency and Frontgrade Gaisler hosted the RISC-V in Space Workshop in Gothenburg, highlighting RISC-V’s advancing role in space applications. Speakers from ESA, AMD, Thales, and others shared insights on HPC, AI, radiation-hardened systems, and open-source hardware—underscoring the architecture’s momentum beyond Earth.

“When you have control of the microarchitecture, you can do a lot to make it safe and ready for space”

“Early on, I saw space emerging as one of the most compelling long-term use cases for RISC-V”, says Asanović, who delivered a talk at the 2021 IEEE Space Computing Conference titled Instruction Sets want to be Free of Gravity. “Missions that span decades demand an ISA that won’t change or vanish. With RISC-V, if your spacecraft’s still running in 50 years the software tools won’t only still work, they’ll have been in active development – with a strong ecosystem and community around them. It’s the foundation space computing needs – and what we set out to build.”

“RISC-V and space have been linked at Microchip from day one,” says Ted Speers, Head of Product Architecture and Planning at Microchip. That link has now evolved into a full-fledged platform for space-grade computing, and a $50 million contract with NASA Jet Propulsion Laboratory (JPLs) for a High Performance Spaceflight Computing (HPSC) platform.

Built around multiple SiFive RISC-V cores, the PIC64-HPSC SoC will feature radiation-hardened variants, built-in fault tolerance, post-quantum cryptography, and vector acceleration for edge AI. The aim? To redefine what’s possible in orbit and beyond. “We’re enabling a spectrum of mission profiles,” explains Speers, “from CubeSats to lunar landers, with compute and fault-tolerance capabilities never before seen in space systems. When you have control of the microarchitecture, you can do a lot to make it safe and ready for space.”

The PIC64-HPSC, incorporating SiFive’s RISC-V cores, is expected to be utilized in virtually every future space mission, including lunar and Mars surface missions. The architecture has already proven itself in orbit – in 2022, a RISC-V-based Microchip PolarFire® SoC flight computer onboard (actually, mounted outside) the ISS performed flawlessly over its 9 month tour, marking a major milestone in the architecture’s transition from research labs to real-world deployment.

Mars is already in the ecosystem’s sights. But for Speers, the bigger picture is about momentum. “Space is a flywheel,” he says. “The more we push with open, adaptable platforms like RISC-V, the faster we spin towards the next frontier. I believe that by 2040, all commercial technology companies will have space strategies.”

“Space continues to inspire many young people,” says Frank Gürkaynak. “One of our Ph.D. students chose to join our team specifically after learning he could work on space-related projects. It’s a field that aligns well with our group’s strengths; in fact, our next space-grade chip is due back from manufacturing any day now.”

Passing the Baton

Given the vast distances in both time and space, it will be today’s young people who ultimately lead the charge into orbit and beyond. Until then, it falls to us to build a culture that draws this next generation of innovators in. On that front, says Frankwell Lin, the RISC-V ecosystem is already much more than the sum of its semiconductors. “For many engineers at Andes, RISC-V isn’t just a platform – it’s a shared culture,” he says. “We’ve participated in every key working group, driven technical debates, and helped ratify specs that shape future chips.”

That culture—open, collaborative, and fiercely future-focused—is what makes RISC-V more than a technology choice. It’s a movement. And like all great movements, its greatest impact may not lie in what it has already achieved, but in what the next 15 years will bring.

15 years is, in both culture and computing terms, a considerable arc. Rewind 15 from 2010 and you’ll find a world without USB, DVDs, or Java – ’Gangsta’s Paradise’ on the radio and Amazon a niche online bookseller. Many of RISC-V’s trailblazers – seasoned veterans with long, successful careers – remain on-scene, having deferred well-earned R&R to help nurture this community. Some have moved on to new pastures; others are sadly no longer with us. Their legacy remains, embedded in the architecture and code that Redmond describes as “the bedrock of computing for generations to come.”

Today, that legacy is inspiring a new wave of innovators through programs like One Student One Chip (OSOC) and Microprocessor for You in Thirty Hours (MYTH). Launched by the University of Chinese Academy of Sciences in 2019, OSOC aims to empower students to graduate with a RISC-V processor chip designed entirely themselves. Through a dynamic mix of theory and hands-on practice, OSOC aims to lower the barriers of RISC-V processor chip design which enables more students to actively engage in every step of the design process, from concept to solving real-world problems. As of May 2025, the total number of OSOC enrollments has exceeded 12,000.

“If a 15-year-old can build a RISC-V processor, imagine what they’ll do in another 15 years”

“Just think what the next generation will have achieved in 15 years, through growing up with RISC-V as their native architecture,” says Professor Yungang Bao, researcher of Institute of Computing Technology (ICT), Chinese Academy of Sciences (CAS). “My students have access to an open, flexible toolset that empowers them to turn bold ideas into working silicon. That’s why I launched OSOC – to enable every student to graduate having designed their own RISC-V chip, experiencing the full design cycle firsthand, from idea to implementation.”

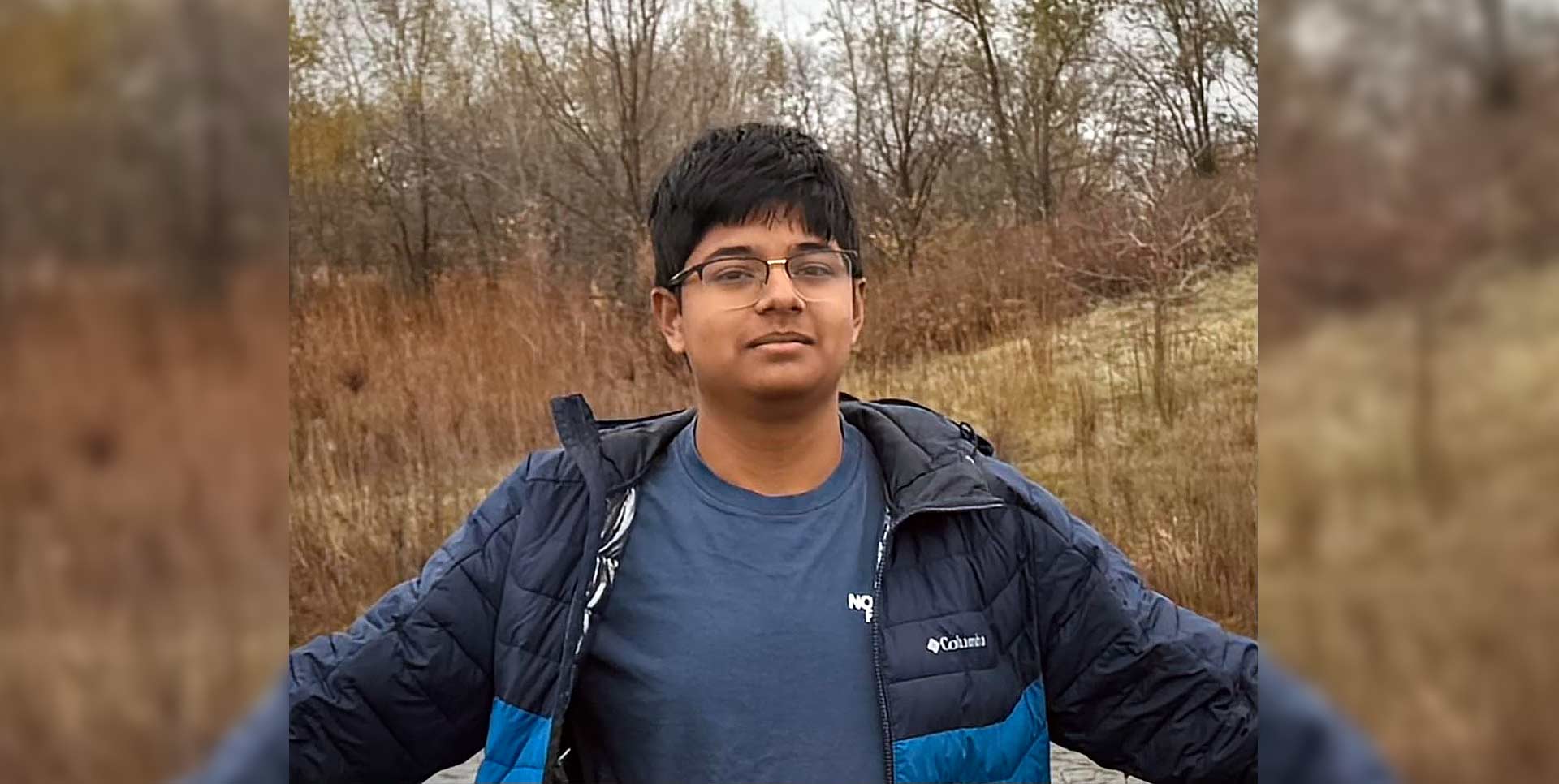

US high school student and MYTH workshop graduate Sonit Sahoo was born shortly before RISC-V was founded in 2010. He’s one of a growing number of teenagers learning how computers work through RISC-V.

“When I was 10, I wrote a platform game for a Commodore64 emulator,” he explains. “I spent months on it. Unfortunately, my excitement fizzled out when I failed to get my hands on a real, working Commodore. Regardless, that project gave me a hunger to build my own hardware to run my programs – and that led me to MYTH.”

MYTH (Microprocessor for You in Thirty Hours) introduced US high schooler Sonit Sahoo to the fundamentals of RISC-V architecture through a structured, youth-focused workshop.

Jointly run by Semiconductor EdTech company VSD and Redwood EDA, the virtual MYTH workshop delivered a structured introduction to RISC-V architecture, covering software-to-hardware concepts through hands-on labs.

“The future of our industry depends on early inspiration,” says Kunal Ghosh, Co-Founder of VSD. “If a 15-year-old can build a RISC-V processor from home using open-source tools, imagine what they might have designed in another 15 years. We’re not just teaching circuits – we’re cultivating confidence, creativity, and a new wave of semiconductor innovators that the world desperately needs.”

“As part of the workshop, I built a custom floating point extension for RISC-V,” says Sahoo. “Beyond the fact that it combined my love for number theory, programming, and hardware design, it really helped my understanding of how computers are built.”

This characteristic, Sahoo says, is the key to RISC-V’s power. “Anyone, from multi-national corporations to hobbyists, can build something powerful and functional with an extremely low barrier to entry. In 15 years I want to have built something with RISC-V that I and anyone who uses it can be proud of. Something that creates a lasting impact on humanity as a whole.”

For Frankwell Lin, this week is more than a milestone – it’s a moment of validation. “RISC-V is ready, proven, and powerful. If you’re building for the future, this is the platform to build on.”

“When I was contemplating doing a PhD in computer architecture, I went to talk to David Wheeler (inventor of the subroutine call) in Cambridge,” recalls Asanović. “He told me there was nothing left to do in computer architecture. If only he could see what we’re doing now.”

“We’re building something many orders of magnitude bigger than what came before. There’s so much to look forward to over the next 15 years. It’s always moving, always interesting, and it’s not slowing down. This story is just beginning.”

.png)